Analog Devices Inc. Sincronizzatore di clock digitalizzato DPLL doppio AD9546

Il sincronizzatore di clock digitalizzato DPLL doppio AD9546 di Analog Devices Inc. combina la tecnologia di clock digitalizzato che trasporta e distribuisce in modo efficiente i segnali di clock nei sistemi. Il clock digitalizzato sull'AD9546 consente la progettazione di sistemi di trasporto clock flessibili e scalabili con allineamento di fase (tempo) ben controllato. AD9546 è ideale per la progettazione di apparecchiature di rete che devono soddisfare i requisiti di sincronizzazione per i clock limite IEEE® 1588™ per ITU-T G.8273.2 classe D. Inoltre, il clock digitalizzato è rilevante anche nelle applicazioni che richiedono il trasporto accurato di frequenza e fase a più endpoint di utilizzo, come la distribuzione di clock di riferimento di sistema sincronizzato (SYSREF) a una matrice di canali ADC.Il sincronizzatore di clock digitale DPLL doppio AD9546 ADI supporta gli standard esistenti ed emergenti dell'Unione internazionale delle telecomunicazioni (ITU) per la fornitura di frequenza, fase e ora della giornata su reti di pacchetti dei fornitori di servizi (ITU-T G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, e ITU-T G.8273.2).

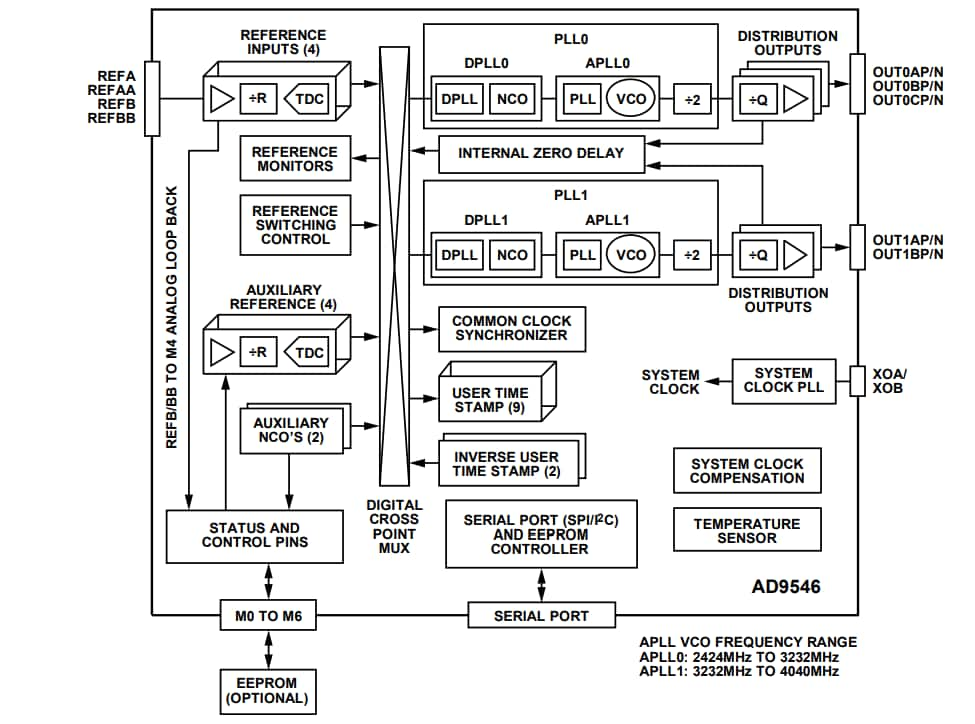

Il dispositivo offre dieci uscite di clock che si sincronizzano con uno qualsiasi degli otto riferimenti di ingresso. Gli anelli ad aggancio di fase (DPLL) digitali riducono il jitter di temporizzazione associato ai riferimenti esterni e agli anelli ad aggancio di fase(APLL) analogici forniscono la traslazione di frequenza con clock di uscita a basso jitter. Il ciclo a controllo digitale e la circuiteria di mantenimento generano in continuo un clock di uscita a basso jitter anche quando tutti gli ingressi di riferimento non funzionano.

L'AD9546 è alloggiato in un package LFCSP a 48 conduttori (7 mm × 7 mm) e opera nell'intervallo di temperatura da -40 °C a +85 °C.

Caratteristiche

- Sottosistema di trasporto clock digitalizzato

- 9 blocchi di UTS indipendenti (timbro orario delle porte di uscita)

- 2 blocchi IUTS indipendenti (timbro orario delle porte di uscita)

- Il DPLL doppio sincronizza i clock dello strato fisico da 1 Hz a 750 MHz, fornendo la traslazione di frequenza con la pulizia del jitter dei riferimenti rumorosi

- Conforme a ITU-T G.8262 e Telcordia GR-253

- Supporta Telcordia GR-1244, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825 e ITU-T G.8273.2

- Monitoraggio in frequenza continua e convalida di riferimento per deviazione di frequenza fino a 50 ppb (5 × 10−8)

- Entrambi i DPLL presentano un divisore frazionario a 24 bit con un modulo programmabile a 24 bit

- Larghezza di banda del filtro ad anello digitale programmabile: da 0,0001 Hz a 1850 Hz

- 2 NCO ausiliari indipendenti e programmabili (da 1 Hz a 65,535 Hz, risoluzione <1,37 phz), adatti per IEEE 1588

- Versione 2 feedback servo nelle applicazioni PTP

- Mantenimento manuale e automatico e commutazione di riferimento, per un funzionamento senza ritardi, senza intoppi o con accumulo di fase

- Commutazione di riferimento programmabile basata su priorità con modalità manuale, supporta modalità rivertiva automatica e non rivertiva automatica

- 5 coppie di pin di uscita clock con ciascuna coppia utilizzabile come LVDS/HCSL/CML differenziale o come 2 uscite a terminazione singola (da 1 Hz a 500 MHz)

- 2 riferimenti di ingresso differenziali o 8 a terminazione singola

- Ingressi di riferimento per interconnessioni mux crosspoint a PLL

- Supporta segnali di clock di ingresso/uscita integrati (modulati)

- Modalità di bloccaggio DPLL veloce

- Fornisce capacità interna per combinare il basso rumore di fase di un risonatore al cristallo o di un oscillatore al cristallo con la stabilità di frequenza e

- precisione di un TCXO o OCXO

- Supporto EEPROM esterno per inizializzazione autonoma

- Singolo funzionamento di alimentazione da 1,8 V con regolazione interna

- Monitoraggio della temperatura integrato, allarme e compensazione della temperatura per prestazioni di ritardo zero migliorate

Applicazioni

- Sincronizzazione ad alta precisione del trasporto di temporizzazione 5G

- Sistema di posizionamento globale (GPS), protocollo temporale di precisione (PTP) (IEEE 1588) e pulizia e sincronizzazione del jitter di SyncE (Synchronous Ethernet)

- Reti di trasporto ottico (OTN), gerarchia digitale sincrona (SDH) e stazioni base a celle macro e piccole

- Clock di piccole stazioni base (banda di base e radio)

- Mantenimento Stratum 2, Stratum 3e e Stratum 3, pulizia jitter e controllo dei transitori di fase

- Supporto JESD204B per il clock di un convertitore analogico/digitale (ADC) e di un convertitore digitale/analogico (DAC)

- Ethernet Carrier

Diagramma a blocchi