Texas Instruments Processore di segnale digitale a punto fisso TMS320VC5501

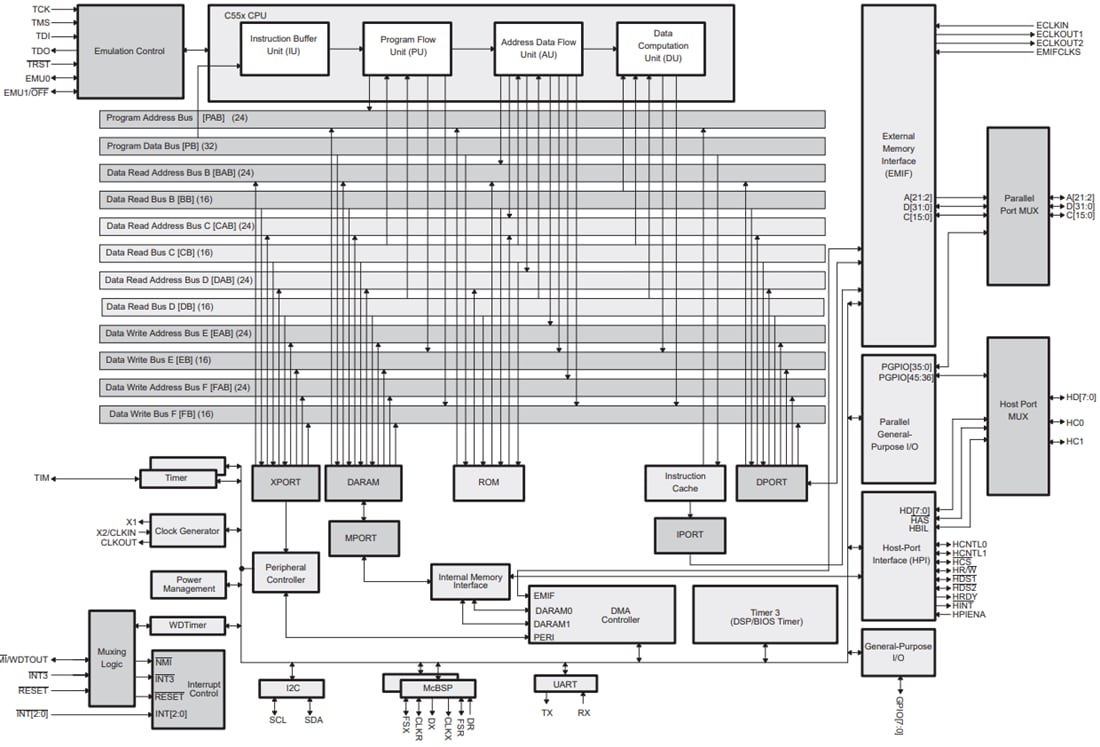

Il processore di segnali digitali (DSP) a punto fisso TMS320VC5501 di Texas Instruments è basato sul core del processore CPU di generazione DSP TMS320C55x. L'architettura DSP TMS320C55x di Texas Instruments raggiunge prestazioni elevate e bassa potenza attraverso un maggiore parallelismo e un'attenzione totale alla riduzione della dissipazione di potenza. La CPU supporta una struttura bus interna composta da un bus di programma, tre bus di lettura dati, due bus di scrittura dati e bus aggiuntivi dedicati all'attività periferica e DMA. Questi bus forniscono la capacità di eseguire fino a tre letture di dati e due scritture di dati, in un unico ciclo. In parallelo, il controller DMA può eseguire fino a due trasferimenti di dati per ciclo indipendentemente dall'attività della CPU.La CPU TMS320C55x fornisce due unità di accumulo moltiplicato (MAC), ciascuna con capacità di moltiplicazione a 17 bit x 17 bit in un singolo ciclo. Un'Unità aritmetica/logica (ALU) a 40 bit centrale è supportata da un'ulteriore unità ALU a 16 bit. L'uso dell'ALU è sotto il controllo del set di istruzioni, fornendo la capacità di ottimizzare l'attività parallela e il consumo di energia. Queste risorse sono gestite nell'unità di indirizzo (AU) e nell'unità di dati (DU) della CPU TMS320C55x. La generazione DSP TMS320C55x supporta un set di istruzioni a larghezza di byte variabile per una migliore densità di codice. L'unità di istruzioni (IU) esegue il recupero del programma a 32 bit dalla memoria interna o esterna e segue le istruzioni per l'unità di programma (PU). L'unità del programma decodifica le istruzioni, dirige le attività alle risorse AU e DU e gestisce la pipeline completamente protetta. La capacità di ramificazione predittiva evita i lavaggi delle condutture durante l'esecuzione delle istruzioni condizionali.

Il set di periferiche TMS320C5501 include un'interfaccia di memoria esterna (EMIF) che fornisce accesso glueless a memorie asincrone come EPROM e SRAM, nonché a memorie ad alta velocità e alta densità come la DRAM sincrona. Le periferiche aggiuntive includono UART, temporizzatore di supervisione e una I-Cache. Due porte seriali con buffer multicanale full-duplex (McBSP) forniscono un'interfaccia glueless a una varietà di dispositivi seriali standard del settore e comunicazione multicanale con un massimo di 128 canali abilitati separatamente. L'interfaccia a porta host (HPI) è un'interfaccia parallela a 8 bit utilizzata per fornire l'accesso del processore host a 16 K di parole di memoria interna sulla 5501. L'HPI opera in modalità multiplexata per fornire un'interfaccia glueless a un'ampia varietà di processori host. Il controller DMA fornisce il movimento dei dati per sei contesti di canale indipendenti senza l'intervento della CPU. Sono inclusi anche due temporizzatori generici, otto pin I/O generici dedicati (GPIO) e la generazione di clock analogico ad anello ad aggancio di fase (APLL).

Caratteristiche

- Processore di segnale digitale (DSP) TMS320C55™ a punto fisso, a bassa potenza e alte prestazioni

- Tempo del ciclo di istruzione di 3,33 ns per velocità di clock di 300 MHz

- Cache istruzioni 16Kbyte (I-Cache)

- Vengono eseguite una/due istruzioni per ciclo

- Doppi moltiplicatori [fino a 600 milioni di accumuli moltiplicatori al secondo (MMAC)]

- Due unità aritmetiche/logiche (ALU)

- Un bus di programma, tre bus interni di lettura dati/operandi e due bus interni di scrittura dati/operazionali

- Cache di istruzioni (16 Kbyte)

- RAM su chip a 16 K × 16 bit composta da quattro blocchi di RAM a doppio accesso a 4 K × 16 bit (DARAM) (32 Kbyte)

- ROM su chip one-wait-state da 16 k × 16 bit (32 Kbyte)

- Spazio di memoria esterno indirizzabile massimo di 8 M × 16 bit

- Memoria bus parallela esterna a 32 bit che supporta l'interfaccia di memoria esterna (EMIF) con capacità di ingresso/uscita per uso generico (GPIO) e interfaccia glueless per

- RAM statica asincrona (SRAM)

- EPROM asincrono

- DRAM sincrono (SDRAM)

- RAM burst sincrono (SBRAM)

- La capacità di emulazione/debug consente di risparmiare le ultime 16 discontinuità del contatore del programma (PC) e i precedenti valori del PC 32

- Controllo programmabile a bassa potenza di sei domini funzionali del dispositivo

- Periferiche su chip

- Controller di accesso diretto alla memoria (DMA) a sei canali

- Due porte seriali con buffer multicanale (McBSPs)

- Generatore di clock ad anello ad aggancio di fase (APLL) analogico programmabile

- Pin I/O (GPIO) per uso generico e un pin di uscita dedicato (XF)

- Interfaccia a porta host parallela (HPI) a 8 bit

- Quattro timer

- Due timer per uso generico a 64 bit

- Temporizzatore di supervisione programmabile a 64 bit

- Contatore DSP/BIOS™ a 64 bit

- Interfaccia circuito inter-integrato (I2C)

- Trasmettitore/ricevitore asincrono universale (UART)

- Logica di emulazione basata su scansione su chip

- Logica di scansione dei confini IEEE Std 1149.1 (JTAG)

- Package

- LQFP (Low-Profile Quad Flatpack) a 176 terminali (suffisso PGF)

- MicroStar BGA™ (Ball Grid Array) a 201 terminali (suffissi GZZ e ZZZ)

- Tensione di alimentazione I/O: 3,3 V

- Tensione di alimentazione del nucleo: 1,26 V

Diagramma a blocchi funzionali