Texas Instruments MCU in tempo reale TMS320F28P65x/TMS320F28P65x-Q1

I microcontroller (MCU) in tempo reale TMS320F28P65x/TMS320F28P65x-Q1 di Texas Instruments appartengono alla famiglia di microcontroller in tempo reale C2000™ di dispositivi scalabili a latenza ultra-bassa. I MCU C2000 sono sviluppati per l'efficienza nell'elettronica di potenza, incluse, a titolo esemplificativo, l'alta densità di potenza e le frequenze di commutazione. Inoltre, i dispositivi supportano l’uso delle tecnologie IGBT, GaN e SiC.Il sottosistema di controllo in tempo reale del microcontroller TMS320F28P65x/TMS320F28P65x-Q1 di TI è basato sul nucleo DSP C28x a 32 bit, che offre 200MIPS di prestazioni di elaborazione del segnale in ciascun nucleo per il funzionamento del codice a galleggiamento o a punto fisso da flash su chip o SRAM. I dispositivi TMS320F28P65x-Q1 sono qualificati AEC-Q100 per applicazioni nel settore automobilistico.

Caratteristiche

- Elaborazione in tempo reale

- Contiene fino a tre CPU: due CPU DSP C28x a 32 bit e una CPU CLA, tutte funzionanti a 200 MHz

- Fornisce una potenza di elaborazione totale equivalente a un dispositivo basato su Arm® Cortex® -M7 da 1.000 MHz su prestazioni della catena di segnale in tempo reale

- Architettura DSP C28x

- Unità FloatingPoint (FPU) a doppia precisione IEEE 754

- Unità matematica trigonometrica (TMU)

- Divisione veloce di interi (FINTDIV)

- Motore e istruzioni CRC (VCRC)

- CPU Control Law Accelerator (CLA)

- Punto a virgola mobile a singola precisione IEEE 754

- Esegue il codice indipendentemente dalle CPU C28x

- Sottosistema analogico

- Tre convertitori analogico/digitale (adc)

- Modalità a 16 bit, 1,19 MSPS ciascuno

- Modalità a 12 bit, 3,92 MSPS ciascuno

- Fino a 40 ingressi a terminazione singola o 19 ingressi differenziali

- Sample-and-hold (S/H) separato su ciascun ADC per consentire misurazioni simultanee

- Post-elaborazione hardware delle conversioni

- Modalità di sovracampionamento hardware (fino a 128x) e sottocampionamento, con accumulo, media e rifiuto dei valori anomali

- 24 canali di ingresso ridondanti per flessibilità

- Confronto automatico dei risultati di conversione per applicazioni di sicurezza funzionale

- 11 comparatori a finestra con riferimenti convertitore digitale/analogico (DAC) a 12 bit

- DAC con compensazione della pendenza: consente il controllo della modalità corrente di picco e corrente di valle

- Opzioni di connessione per sensore di temperatura interno e riferimento ADC

- Due uscite DAC bufferizzate a 12 bit

- Due Controller Area Network CAN FD/MCAN con velocità dati flessibile

- Tre convertitori analogico/digitale (adc)

- Periferiche di sistema

- Due controller di accesso diretto alla memoria (DMA) a 6 canali

- 185 pin di ingresso/uscita per uso generico (GPIO) multiplexati individualmente programmabili

- Controller di interruzione periferica esteso (ePIE)

- Supporto della modalità a bassa potenza (LPM)

- Analisi e diagnostica in tempo reale integrata (ERAD)

- CRC background (BGCRC)

- Periferiche di sicurezza

- Acceleratore standard di crittografia avanzato (AES-128, 192, 256)

- Sicurezza

- JTAGLOCK

- Avvio a zero pin

- Sicurezza a doppia zona

- Numero di identificazione univoco (UID)

- Periferiche di sicurezza

- Implementazione più semplice con confronto reciproco

- Lockstep sulla CPU C28x 2

- Autotest all'attivazione della memoria (MPOST)

- Autotest integrato nell'hardware (HWBIST)

- Conforme alla sicurezza funzionale in modo mirato

- Sviluppato per applicazioni di sicurezza funzionale

- La documentazione sarà disponibile per aiutare la progettazione del sistema ISO 26262 e IEC 61508

- Capacità sistematica fino ad ASIL e D/SIL-3 mirata

- Capacità hardware fino ad ASIL B e SIL 2 mirata

- Certificazione di sicurezza

- Certificazione ISO 26262 e IEC 61508 fino a ASIL B e SIL 2 di TÜV SÜD prevista

- Clock e controllo di sistema

- Due oscillatori interni da 10 MHz

- Oscillatore al cristallo integrato su chip

- 2*APLL, BOR, RAM vettoriale di interruzione ridondante

- Modulo temporizzatore del sistema di controllo in modalità a finestra

- Circuito di rilevamento clock mancante

- Comparatore a doppio clock (DCC)

- Aggiornamento Firmware Live (LFU)

- Passaggio rapido dal vecchio al nuovo FirmWare con o senza ciclo di accensione

- Core a 1,2 V, progettazione I/O a progettazione I/O a 3,3 V

- VREG interno per generazione da 1,2 V

- Circuito di ripristino interruzione di corrente (BOR)

- Memoria

- 1,28 MB di flash mappabile alla CPU (protezione ECC) con cinque banchi flash

- 248 KB di RAM (potenziata con protezione della parità)

- Interfaccia di memoria esterna (EMIF) con ASRAM, supporto SDRAM o ASIC/FPGA

- Periferiche di controllo

- 36 canali del modulatore di larghezza di impulso (PWM), tutti con capacità ad alta risoluzione di 150 ps (HRPWM)

- Supporto della logica di banda morta minima (MINDB), della logica combinata illegale (ICL) e di altre funzionalità speciali (ovvero, emulazione diodi [DE])

- Supporto di convertitori a matrice, convertitori multilivello e convertitori risonanti senza ulteriore logica esterna

- Sette moduli di acquisizione potenziata (eCAP)

- Su due dei sette moduli eCAP è disponibile l'acquisizione ad alta risoluzione (HRCAP)

- Due nuove unità di monitoraggio per fronte, larghezza di impulso e periodo di accoppiamento con flash ePWM ed eventi di sgancio

- Aumento di 256 ingressi per maggiori opzioni di acquisizione

- Nuova capacità di generazione SoC ADC

- L’eCAP può essere utilizzato anche per PWM aggiuntivo

- Sei moduli Enhanced Quadrature Encoder Pulse (eQEP).

- 16 canali di ingresso del modulo filtro Sigma-Delta (SDFM), due filtri indipendenti per canale

- Generatore di schema integrato (EPG)

- Blocco logico configurabile

- Sei riquadri logici per aumentare la capacità periferica esistente o definire una logica personalizzata per ridurre o rimuovere CPLD/FPGA esterni

- Supporta le interfacce Encoder senza la necessità di FPGA

- Consente la generazione PWM personalizzata per la conversione di potenza

- 36 canali del modulatore di larghezza di impulso (PWM), tutti con capacità ad alta risoluzione di 150 ps (HRPWM)

- Periferiche di comunicazione

- Controller (ESC) EtherCAT® SubordinateDevice (o SubDevice)

- USB 2.0 (MAC + PHY)

- Interfaccia seriale rapida (FSI) che consente lo scambio di dati fino a 200 Mbps attraverso l’isolamento

- Quattro porte SPI ad alta velocità (fino a 50 MHz)

- Quattro interfacce di comunicazione seriale (SCI) (supporto UART)

- Due ricevitori/trasmettitori asincroni universali (UART) ad alta velocità (25 Mbps)

- Due interfacce I2C (400 kbps)

- Opzione di avvio esterno via SPI/SCI/I2C

- Due moduli di rete locale di interconnessione (LIN) compatibili con UART (supporto SCI)

- Interfaccia Power-Management Bus (PMBus) (supporta I2C)

- Un Area Network Controller (CAN/DCAN)

- opzioni di package:

- Imballaggio ecologico e senza piombo

- Nuovo Ball Grid Array a passo fine da 256 sfere (nFBGA) [suffisso ZEJ], passo 13 mm × 13 mm/0,8 mm

- PowerPAD™ a 176 pin Quad Flatpack a basso profilo termicamente ottimizzato (HLQFP) [suffisso PTP], passo 26 mm × 26 mm/0,5 mm

- Nuovo Fine Pitch Ball Grid Array (nFBGA) da 169 sfere [suffisso NMR], passo 9 mm × 9 mm/0,65 mm

- PowerPAD® a 100 pin sottile termicamente avanzato

- Quad Flatpack (HTQFP) [suffisso PZP], passo 16 mm × 16 mm/0,5 mm

- Temperatura ambiente (TA) da -40 °C a 125 °C (qualifica per i settori industriale e automobilistico)

Applicazioni

- Modulo di controllo unità servo

- Servomotore robot

- Controllo CNC

- Controllo dei motori dei robot mobili

- Controllo motore commerciale di grandi dimensioni alta tensione CA

- Controller del segmento motore lineare

- Inverter centrale

- Inverter di stringa

- Sistema di conversione di potenza

- Stazione di ricarica rapida CC

- Invertitore e controllo motore

- CA-CC industriale

- UPS trifase

- UPS online monofase

- PSU per server e reti commerciali

- Scheda integrata (OBC) e caricabatterie wireless

- Modulo compressore HVAC di tipo automobilistico

- Fanale anteriore

Schede tecniche

Video

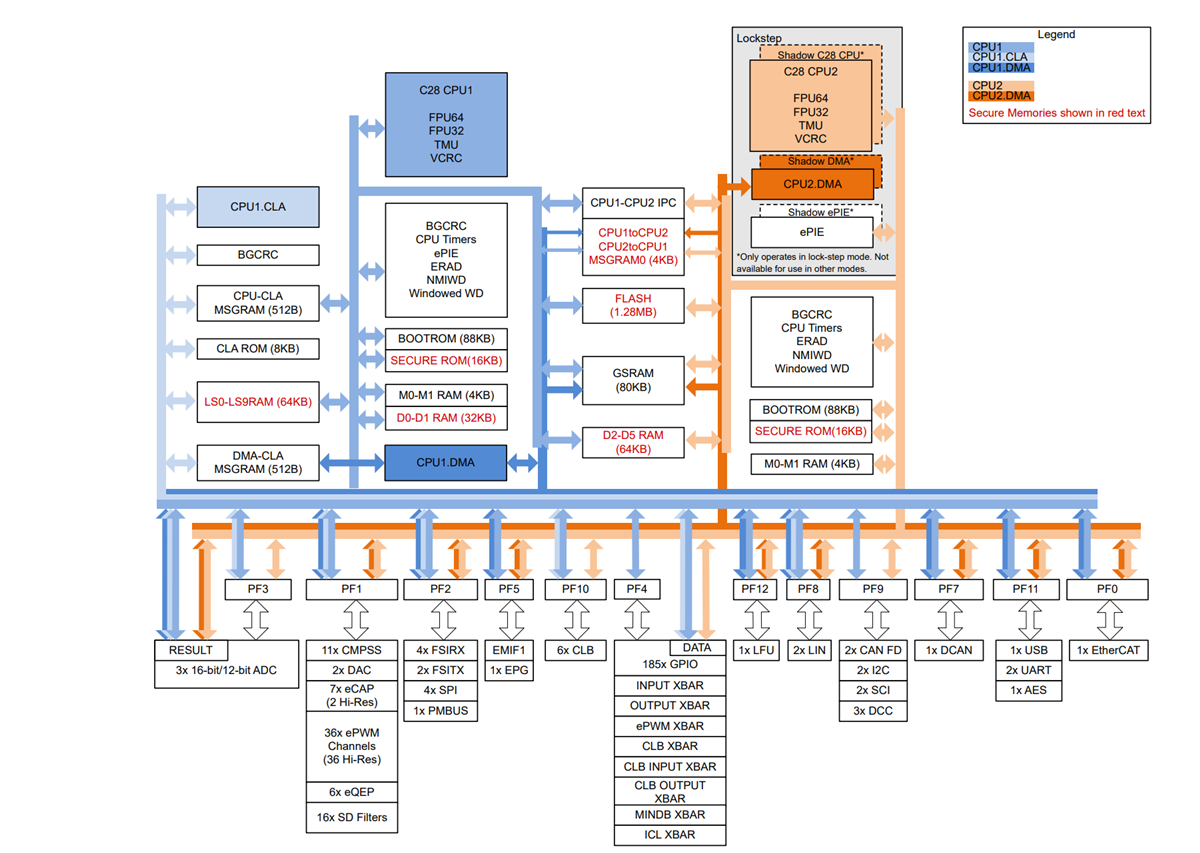

Diagramma a blocchi funzionale

Pubblicato: 2023-12-28

| Aggiornato: 2026-02-06