Texas Instruments Buffer Clock LVDS con uscita a 8 canali LMK1D1208P

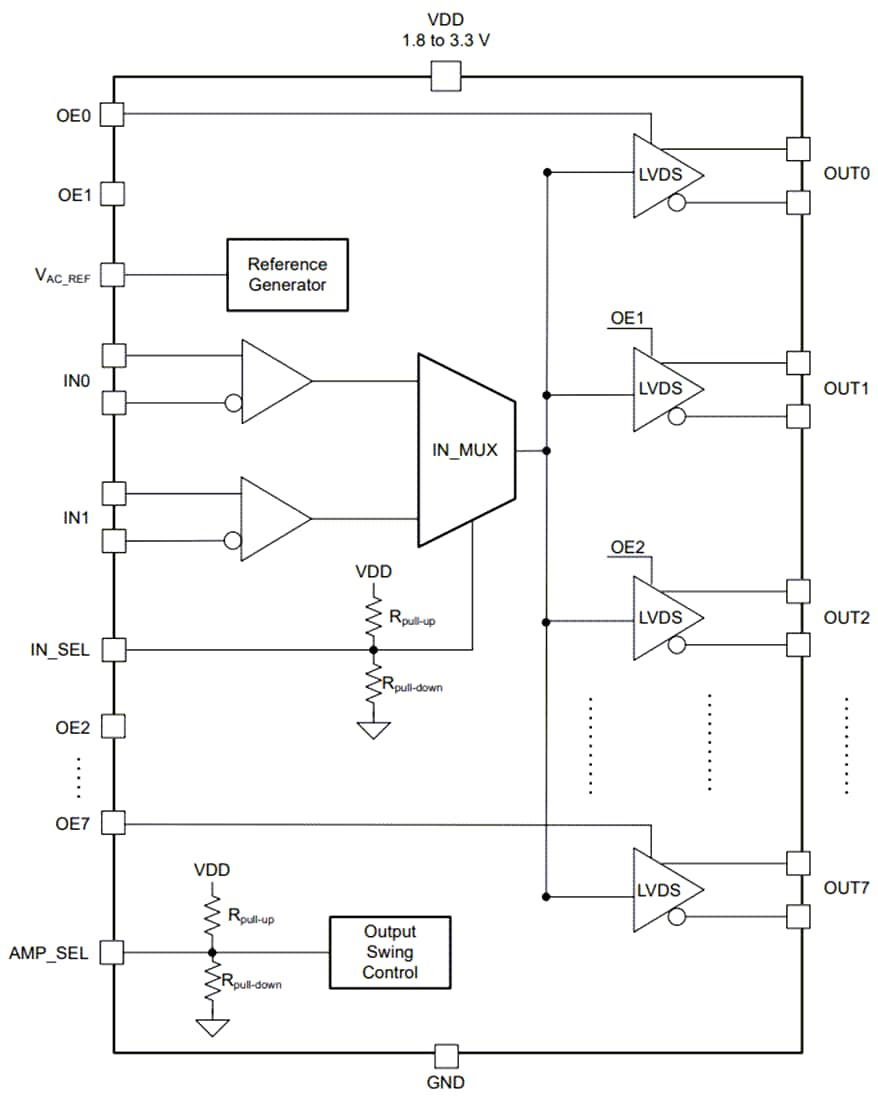

Il buffer di clock LVDS con uscita a 8 canali LMK1D1208P di Texas Instruments distribuisce uno dei due ingressi di clock selezionabili (IN0 e IN1) a otto coppie di uscite di clock LVDS differenziali (da OUT0 a OUT7). Questa distribuzione avviene con un minimo sfasamento per la distribuzione del clock. Gli ingressi possono essere LVDS, LVPECL, LVCMOS, HCSL o CML.LMK1D1208P di Texas Instruments è specificamente progettato per pilotare linee di trasmissione da 50 Ω. Inoltre, quando gli utenti gestiscono gli ingressi in modalità a terminazione singola, devono applicare la tensione di polarizzazione appropriata al pin di ingresso negativo non utilizzato. Il pin IN_SEL seleziona l'ingresso, che viene indirizzato alle uscite. Il componente supporta una funzione di ingresso di sicurezza. Il dispositivo integra inoltre un'isteresi di ingresso che previene l'oscillazione casuale delle uscite in assenza di un segnale di ingresso.

Ogni uscita differenziale LVDS è abilitata impostando il pin OEx corrispondente su una logica alta 1. Se questo pin è impostato su una logica a basso 0, l'uscita è disabilitata in stato Hi-Z con conseguente riduzione del consumo energetico. Il dispositivo opera in un ambiente di alimentazione da 1,8 V, 2,5 V o 3,3 V ed è caratterizzato da una temperatura ambiente da –40 °C a 105 °C.

Caratteristiche

- Famiglia di buffer di clock LVDS ad alte prestazioni con due ingressi e otto uscite (2:8)

- Frequenza di uscita fino a 2 GHz

- Pin hardware per attivazione/disattivazione uscita singola

- Tensione di alimentazione 1,8 V/2,5 V/3,3 V ± 5%

- Basso jitter aggiuntivo (< 60 fs rms massimo in 12 kHz a 20 MHz a 156,25 MHz)

- Rumore di fase molto basso di -164 dBc/Hz (tipico)

- Ritardo di propagazione molto basso < 575 ps max.

- Sfasamento di uscita massimo di 20 ps

- Ingressi a sicurezza intrinseca

- Gli ingressi universali accettano LVDS, LVPECL, LVCMOS, HCSL e CML

- Tensione di riferimento LVDS, VCA_REF, disponibile per ingressi accoppiati capacitivi

- Intervallo di temperatura industriale da -40 °C a +105 °C

- Package VQFN a 40 pin da 6 mm × 6 mm

Applicazioni

- Telecomunicazioni e collegamenti in rete

- Diagnostica per immagini

- Test e misurazioni

- Infrastruttura wireless

- Audio, video e segnaletica professionale

Schema a blocchi funzionale