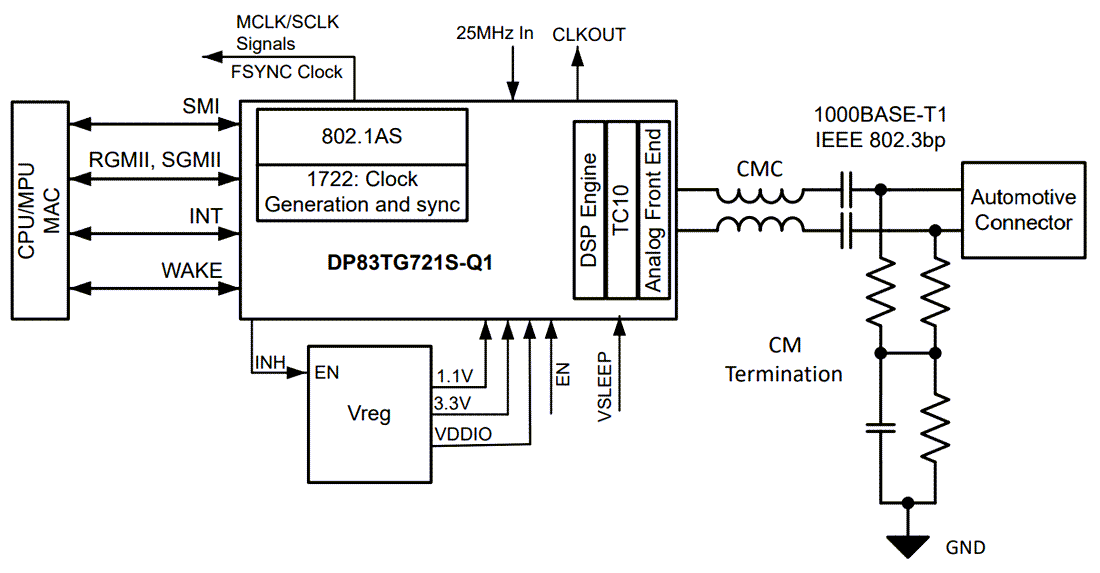

Texas Instruments Ricetrasmettitore PHY Ethernet DP83TG721-Q1 1000Base-T1

Texas Instruments DP83TG721-Q1 1000Base-T1 Ethernet PHY Transceiver is an IEEE 802.3bp and Open Alliance transceiver that provides all physical layer functions needed to receive and transmit data over unshielded/shielded single twisted-pair cables. The device offers xMII flexibility with support for RGMII and SGMII MAC interfaces. DP83TG721-Q1 supports the OA TC10 low-power sleep feature (with wake forwarding) to reduce system power consumption when communication is not required. This device offers the Diagnostic Tool Kit, with an extensive list of real-time monitoring tools, debug tools and test modes.Il DP83TG721-Q1 di Texas Instruments integra la marcatura temporale hardware IEEE 1588v2/802.1AS e il PLL frazionario, consentendo una sincronizzazione temporale estremamente precisa.Il Il PLL frazionario consente la sincronizzazione di frequenza/fase del Wall clock, eliminando la necessità di un VCXO esterno e generando un'ampia gamma di frequenze sincronizzate nel tempo, necessarie per applicazioni audio, video e altre applicazioni ADAS. Il DP83TG721-Q1 integra anche la decodifica IEEE 1722 CRF per generare un media clock (wall clock sincronizzato) per AVB e altri standard audio. Il DP83TG721-Q1 può anche generare sincronizzazione F/SCLK (clock parete sincronizzato) per l'interfaccia I2S/TDM8 necessaria per le applicazioni audio.

Il DP83TG721-Q1 è compatibile con i PHY 100BASE-T1 e 1000BASE-T1 di TI, consentendo la scalabilità del progetto con una singola scheda per entrambe le velocità.

Caratteristiche

- Conforme a IEEE 802.3bp 1000BASE-T1

- Conforme a OA TC10, < corrente di riposo < 20 µA

- Sveglia locale e remota e wake-forwarding

- TSN avanzato

- Sincronizzazione temporale IEEE 1588v2/802.1AS•

- Marcatura temporale hardware con correzione di fase integrata

- Segnale di 1pps altamente preciso (±15 ns)

- Clock audio

- Capacità di generazione del clock multimediale AVB IEEE 1722

- Uscita orologio a parete sincronizzata in fase da 1KHz a 50MHz

- Generazione di clock SCLK/FSYNC/MCLKI2Se TDM8

- Interoperabilità Open Alliance TC12 e conformità EMC

- Conformità OA EMC

- Conforme a EMC SAE J2962-3

- LPF integrato su pin MDI

- Interfacce MII, RMII, RGMII e SGMII MAC

- Tensioni I/O supportate di 3,3 V, 2,5 V, e 1,8 V

- Pin compatibile con i PHY 100BASE-T1 e 1000BASE-T1 di TI

- Progettazione di una singola scheda per 100BASE-T1 e 1000BASE-T1 con modifica della distinta base richiesta

- Kit strumento diagnostico

- Monitoraggio temperatura, tensione, ESD

- Calcolatore del throughput dei dati con generatore di pacchetti MAC incorporato, contatore e controllore di errori.

- Indicatore di qualità del segnale

- Rilevamento dei guasti dei cavi aperti e corti basato su TDR

- CQI per il monitoraggio del degrado dei cavi

- Modalità di ritorno

- Conformi alle qualifiche AEC-Q100

- IEC61000-4-2 ESD (scarica di contatto ±8 kV)

Applicazioni

- Unità di controllo telematica (TCU, TBOX)

- AVB

- ADAS (LiDAR, RADAR, telecamera anteriore)

- Controllo zonale, di porta e di corpo

Schema semplificato