Texas Instruments Processori AM654x/AM652x basati su ARM™

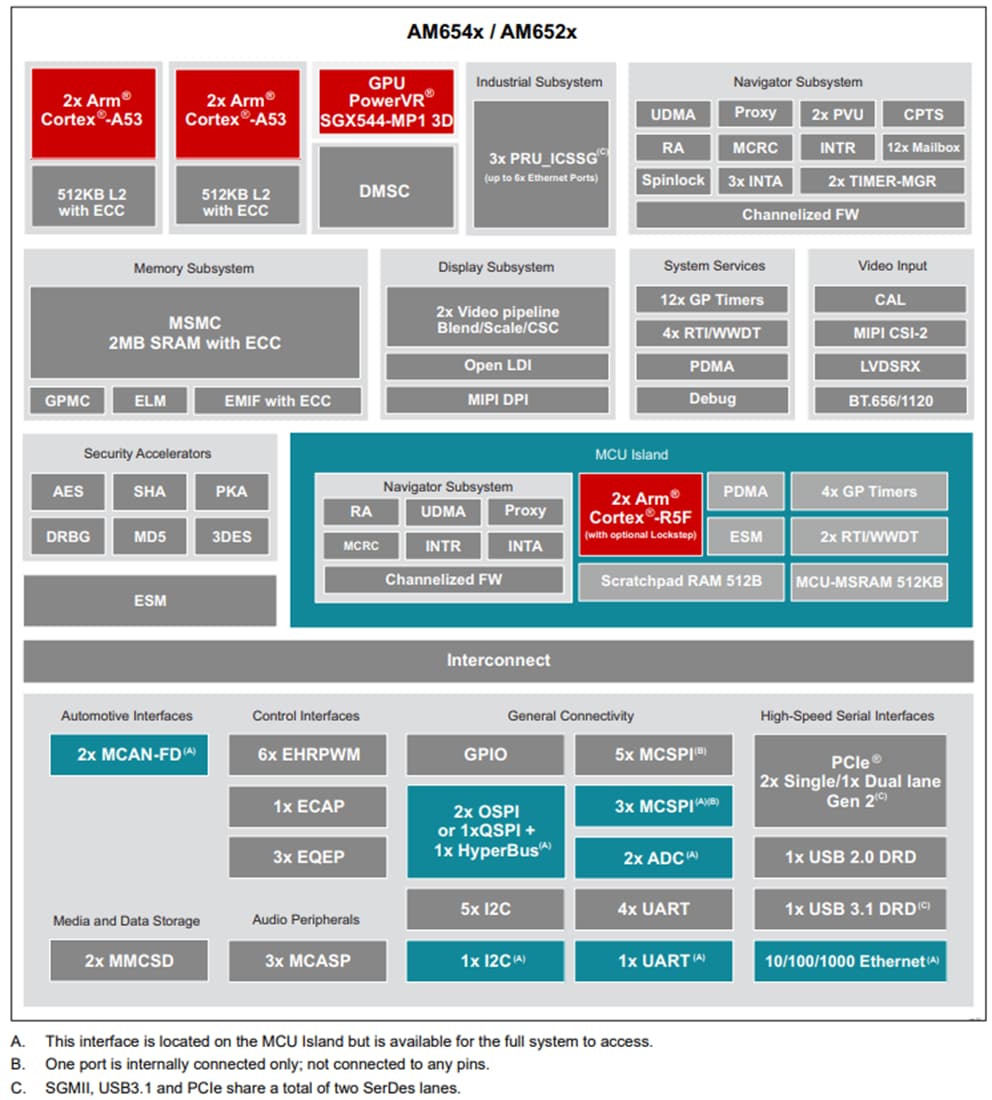

I processori AM654x/AM652x basati su ARM™di Texas Instruments sono destinati ad applicazioni ARM® e realizzati per soddisfare le complesse esigenze di elaborazione dei moderni prodotti embedded per Industry 4.0. I dispositivi AM652x e AM654x combinano due o quattro core ARM® Cortex®-A53 con un doppio sottosistema MCU Arm Cortex-R5F. Questi includono caratteristiche volte ad aiutare i clienti a raggiungere obiettivi funzionali di sicurezza per i prodotti finali. Include anche tre sottosistemi di comunicazione industriale Gigabit (PRU_ICSSG) per creare un SoC in grado di eseguire controlli industriali ad alte prestazioni con connettività industriale ed elaborazione per applicazioni di sicurezza funzionale. AM65xx è attualmente in fase di valutazione per ottenere la certificazione da parte di TÜV SÜD secondo IEC 61.508.I quattro nuclei Arm Cortex-A53 dell'AM654x sono disposti in due cluster dual-core con memoria L2 condivisa per creare due canali di elaborazione. I due nuclei Arm Cortex-A53 nell'AM652x sono disponibili in un singolo cluster dual-core e due opzioni di cluster single-core. L'ECC completo è incluso nella memoria su chip, nelle periferiche e nell'interconnessione per garantire affidabilità. Il SoC, nel suo complesso, presenta caratteristiche che aiutano i clienti a progettare sistemi in grado di raggiungere obiettivi di sicurezza funzionali. Accelerazione crittografica e avvio sicuro sono disponibili su alcuni dispositivi AM654x e AM652x, oltre ai firewall granulari gestiti dal DMSC.

Le CPU RISC Arm Cortex-A53 offrono programmabilità con estensione Arm Neon™. Il doppio sottosistema MCU Arm Cortex-R5F è disponibile per uso generico come due nuclei o può essere utilizzato in lockstep per soddisfare le esigenze delle applicazioni di sicurezza funzionale. I sottosistemi PRU_ICSSG possono essere utilizzati per fornire fino a sei porte Ethernet industriale come Profinet IRT, TSN, Ethernet/IP o EtherCAT (tra molti altri), o possono essere utilizzati per la connettività Gigabit Ethernet standard.

Texas Instruments fornisce una serie completa di strumenti software e di sviluppo per i core Arm, tra cui processore SDK Linux, Linux-RT, RTOS, Android, compilatori C e un'interfaccia di debug per la visibilità nell'esecuzione del codice sorgente. La documentazione di sicurezza funzionale e di sicurezza applicabile sarà messa a disposizione per assistere i clienti nello sviluppo di sistemi di sicurezza funzionale o relativi alla sicurezza.

Caratteristiche

- Core del processore

- Sottosistema microprocessore dual-core o quad-core Arm Cortex-A53 fino a 1,1 GHz

- Fino a due cluster a nucleo doppio o due a nucleo singolo Arm Cortex-A53 con cache L2 da 512 KB, incluso SECDED

- Ogni nucleo A53 ha 32 KB di ICache L1 e 32 K di DCache L1

- Arm Cortex-R5F a due nuclei fino a 400 MHz

- Supporta la modalità lockstep

- ICache da 16 KB, DCache da 16 KB e RAM da 64 KB per nucleo R5F

- Sottosistema microprocessore dual-core o quad-core Arm Cortex-A53 fino a 1,1 GHz

- Sottosistema industriale

- Tre sottosistemi di comunicazione industriale gigabit (PRU_ICSSG)

- Fino a due porte Ethernet 10/100/1000 per PRU_ICSSG

- Supporta due porte SGMII

- Compatibilità con PRU-ICSS da 10/100 Mb

- 24 PWM per PRU_ICSSG

- Controllo ciclo per ciclo

- Migliore controllo dell'intervento

- 18 filtri Sigma-delta per PRU_ICSSG

- Logica di corto circuito

- Logica di sovracorrente

- 6 interfacce di codificatore di posizione multi-protocollo per PRU_ICSSG

- Tre sottosistemi di comunicazione industriale gigabit (PRU_ICSSG)

- Sottosistema di memoria

- Fino a 2 MB di RAM L3 su chip con SECDED

- Controller di memoria condiviso multicore (MSMC)

- SRAM fino a 2 MB (2 banchi × 1 MB) con SECDED

- SRAM con mappatura della memoria condivisa di livello 2 o 3

- Cache di livello 3 coerente condivisa

- Bus porta processore a 256 bit e bus indirizzo fisico a 40 bit

- Interfacce bidirezionali coerenti e unificate per connettersi a processori o master di dispositivi

- Pre-riscaldamento cache L2, L3 e post-flushing

- Gestione della larghezza di banda con vincoli di avviamento

- Un'interfaccia master dell'infrastruttura

- Interfaccia master di memoria esterna singola

- Supporta il sistema virtuale distribuito

- Supporta il motore DMA interno – Unità di instradamento dati (DRU)

- Protezione da errore ECC

- SRAM fino a 2 MB (2 banchi × 1 MB) con SECDED

- Sottosistema DDR (DDRSS)

- Supporta tipi di memoria DDR4 fino a DDR-1600

- Bus dati a 32 bit e bus SECDED a 7 bit

- 8 GB di spazio indirizzabile totale

- Controller di memoria per uso generico (GPMC)

- Componente semiconduttore SafeTI™

- Progettato per applicazioni di sicurezza funzionale

- Sviluppato secondo i requisiti di IEC 61508

- Raggiunge l'integrità sistematica di SIL-3

- Per l'isola di sicurezza MCU, è inclusa una diagnostica sufficiente per ottenere i requisiti di integrità dei guasti casuali di SIL-2

- Per il resto del SoC, è inclusa una diagnostica sufficiente per ottenere i requisiti di integrità dei guasti casuali di SIL-2

- Inoltre, sono stati predisposti parametri architettonici sufficienti per ottenere l'esecuzione delle applicazioni SIL-3 in base a un concetto di sicurezza adeguato (ad esempio, confronto reciproco per software)

- Manuale di sicurezza funzionale disponibile

- Certificazione di sicurezza

- Certificazione di sicurezza funzionale a livello di componente di TÜV SÜD [certificazione in corso]

- Caratteristiche di sicurezza funzionale

- ECC o controllo di parità sulle memorie critiche e interconnessione bus interna

- Firewall per contribuire a fornire assenza di interferenze (FFI, Freedom From Interference)

- Test automatico (BIST) integrato per CPU, timer di fascia alta e RAM su chip

- Supporto per iniezione errore hardware per test diagnostici

- Moduli di segnalazione di errore (ESM) per l'acquisizione di errori funzionali relativi alla sicurezza

- Tensione, temperatura e controllo clock

- Timer watchdog a finestra e non in più domini di clock

- Isola MCU

- Isolamento del sottosistema microprocessore dual-core Arm Cortex-R5F

- Tensione separata, clock, reset e periferiche dedicate

- Collegamento MCSPI interno al resto del SoC

- Sicurezza

- Avvio protetto supportato

- Root-of-trust applicata all'hardware

- Supporto per cambiare la root-of-trust tramite chiave di backup

- Supporto per protezione da rilevamento, protezione IP e protezione anti-rollback

- Accelerazione crittografica supportata

- Motore crittografico sensibile alle sessioni con la capacità di commutare automaticamente il materiale chiave in base al flusso di dati in entrata

- Supporta nuclei crittografici

- AES – Dimensioni chiave 128/192/256 bit

- 3DES – Dimensioni chiave 56/112/168 bit

- MD5, SHA1

- SHA2 -224/256/384/512

- DRBG con un vero generatore numerico casuale

- PKA (Public Key Accelerator) per assistere nell'elaborazione RSA/ECC

- Supporto DMA

- Sicurezza del debug

- Accesso sicuro al debug controllato dal software

- Debug con funzionalità di sicurezza

- Ambiente di esecuzione affidabile (TEE) supportato

- TEE basato su Arm TrustZone

- Ampio supporto del firewall per l'isolamento

- Percorso e interconnessione DMA sicuri

- Watchdog/timer/IPC sicuro

- Supporto di archiviazione sicuro

- Supporto di crittografia e autenticazione on-the-fly per l'interfaccia OSPI

- Supporto della sicurezza di rete per la crittografia/l'autenticazione dei dati (payload) tramite motore hardware crittografico basato su pacchetti

- Coprocessore di sicurezza (DMSC) per la gestione delle chiavi e della sicurezza, con livello di dispositivo dedicato, interconnessione per software di sicurezza

- Avvio protetto supportato

- Servizi SoC

- Controller di sicurezza per la gestione dei dispositivi (DMSC)

- Controller di sistema SoC centralizzato

- Gestisce servizi di sistema, tra cui avvio iniziale, sicurezza, sicurezza funzionale e gestione clock/reset/alimentazione

- Controller di gestione dell'energia per modalità attive e a bassa potenza

- Comunicazione con varie unità di elaborazione tramite gestione messaggi

- Interfaccia semplificata per ottimizzare le periferiche inutilizzate

- Capacità di tracciamento e debug

- Sedici timer a 32 bit per uso generico

- Due sottosistemi di navigazione per il movimento e il controllo dei dati (NAVSS)

- Acceleratore ad anello (RA)

- DMA unificato (UDMA)

- Fino a 2 Timer Manager (TM) (1024 timer ciascuno)

- Controller di sicurezza per la gestione dei dispositivi (DMSC)

- Multimedia

- Sottosistema display

- Due manager di overlay completamente mappati in ingresso associati a due uscite di visualizzazione

- Interfaccia parallela DPI MIPI a una porta

- Una porta OLDI

- Unità di elaborazione grafica 3D (GPU) SGX544-MP1 PowerVR

- Una videocamera a interfaccia seriale-2 (MIPI CSI-2)

- Una porta di acquisizione video: BT.656/1120 (senza sincronizzazione integrata)

- Sottosistema display

- Interfacce ad alta velocità

- Un'interfaccia Gigabit Ethernet (CPSW) che supporta

- RMII (10/100) o RGMII (10/100/1000)

- IEEE1588 (Allegato D, Allegato E, Allegato F 2008) con 802.1AS PTP

- Bridging audio/video (P802.1Qav/D6.0)

- Ethernet a risparmio energetico (802.3az)

- Jumbo frame (2024 byte)

- Gestione PHY MDIO secondo la clausola 45

- Due sottosistemi PCI-Express (PCIe) revisione 3.1

- Supporta il funzionamento Gen2 (5,0 GT/s)

- Due porte indipendenti a 1 canale o una singola porta a 2 vie

- Supporto per funzionamento root-complex ed end-point simultaneo

- Sottosistema Dual-Role Device (DRD) USB 3.1

- Una porta Gen1 SuperSpeed migliorata

- Una porta USB 2.0

- Ogni porta è configurabile in modo indipendente come host USB, periferica USB o DRD USB

- Un'interfaccia Gigabit Ethernet (CPSW) che supporta

- Connettività generale

- 6 porte a circuito inter-integrato (I2C™)

- 5 moduli UART/IrDA/CIR configurabili

- Due interfacce flash simultanee configurate come

- Due interfacce flash OSPI

- o interfaccia HyperBus™ e flash OSPI1

- 2 convertitori da analogico a digitale a 12 bit (ADC)

- Fino a 4 M campioni/sec

- Otto ingressi analogici multiplati

- 8 controller per interfacce periferiche seriali multicanale (MCSPI)

- Due con connessioni interne

- Sei con interfacce esterne

- Pin I/O per uso generico (GPIO)

- Interfacce di controllo

- 6 moduli potenziati per modulatore a larghezza di impulso (EHRPWM) ad alta risoluzione

- Un modulo ECAP (Enhanced Capture)

- 3 moduli EQEP (Enhanced Quadrature Encoder Pulse)

- Interfacce automotive

- 2 moduli modulari Controller Area Network (MCAN) con supporto CAN-FD completo

- Interfacce audio

- 3 moduli porta seriale audio multicanale (MCASP)

- Storage per dati e file multimediali

- 2 interfacce Multimedia Card™/Secure Digital (MMC™/ SD)

- Gestione dell'alimentazione semplificata

- Sequenza di alimentazione semplificata con supporto completo per I/O a doppia tensione

- Gli LDO integrati riducono la complessità della soluzione di alimentazione

- LDO SDIO integrato per gestire la transizione automatica della tensione per l'interfaccia SD

- Generazione del reset all'accensione (POR) integrata che riduce la complessità della soluzione di alimentazione

- Supervisore di tensione integrato per monitoraggio della sicurezza funzionale

- Rilevatore glitch di alimentazione integrato per rilevare transitori di alimentazione rapidi

- Integrazione analogica/sistema

- Rilevamento VBUS USB integrato

- I/O a sicurezza intrinseca per RIPRISTINO DDR

- Tutti i driver dei pin I/O disabilitati durante il ripristino per evitare conflitti bus

- Disattivazione I/O predefinita durante il reset per evitare conflitti di sistema

- Supporto del cambiamento dinamico di configurazione I/O pinmux

- Architettura System-on-Chip (SoC)

- Supporta l’avvio primario da interfacce UART, I2C, OSPI, HyperBus, NOR Flash parallele, SD o EMMC™, USB, PCIe ed Ethernet

- Tecnologia CMOS 28 nm

- 23 mm × 23 mm, passo di 0,8 mm, FCBGA (ACD) a 784 pin

Applicazioni

- Controller logici programmabili (PLC) industriali

- Automazione di fabbrica con funzioni di sicurezza

- Comunicazioni bus multi-protocollo

- PC industriali

- Robot industriali

- Interfaccia uomo macchina (HMI)

- Relè di protezione infrastruttura di rete

- Unità di azionamento motore robotiche

Video

Diagramma a blocchi funzionale