NXP Semiconductors PMIC a uscita multipla VR5510

I PMIC a uscita multipla per l'automotive VR5510 di NXP Semiconductors sono progettati per applicazioni gateway, ADAS, V2X e infotainment Il VR5510 comprende molteplici modalità per gli interruttori ad alta efficienza e i regolatori di tensione lineare. I PMIC forniscono la sincronizzazione della frequenza esterna su ingressi e uscite per prestazioni ottimizzate del sistema EMC.I PMIC a uscita multipla VR5510 di NXP Semiconductors per il settore automotive presentano caratteristiche di sicurezza migliorate con uscite a prova di guasto e coprono i livelli di integrità di sicurezza ASIL B e ASIL D. Il VR5510 può essere pienamente implementato in un sistema di partitioning orientato alla sicurezza e può anche essere configurato per funzionare come parte della versione QM non di sicurezza.

Il VR5510 è disponibile in diverse versioni che supportano varie applicazioni di sicurezza e presentano numerose opzioni per il numero di guide di uscita, impostazioni della tensione di uscita, frequenze di funzionamento e sequenziamento di accensione.

Il VR551, se offerto nel package QFN56, ha fianchi termicamente bagnabili e potenziati. I dispositivi con fianchi bagnabili consentono l’ispezione ottica automatica (AOI), mostrano una maggiore resistenza alle forze di taglio e possono gestire la flessione della PCB, migliorando così l’affidabilità.

Caratteristiche

- Tensione di ingresso massima 60 VCC

- Controller buck sincrono VPRE con MOSFET esterni

- Tensione di uscita configurabile, frequenza di commutazione e capacità di corrente fino a 10 A

- Convertitori BUCK1 e BUCK2 sincroni e integrati a bassa tensione dedicati all’alimentazione del nucleo MCU con capacità SVS/DVS

- Tensione di uscita configurabile e capacità di corrente fino a 3,6 A di picco; funzionamento bifase per estendere la capacità di corrente fino a 7,2 A di picco

- Convertitore BUCK3 sincrono integrato a bassa tensione

- Tensione di uscita configurabile e capacità di corrente fino a 3,6 A di picco

- Convertitore boost con interruttore lato basso integrato

- Tensione di uscita configurabile e capacità di corrente di ingresso fino a 2,25 A di picco

- 3 regolatori di tensione lineari (LDOx) per forniture IO MCU, DDR e ADC

- Tensione di uscita configurabile e capacità di corrente fino a 400 mA

- Regolatore lineare ad alta tensione (HVLDO) con capacità di corrente fino a 10 mA in modalità LDO e 100 mA in modalità commutazione

- Tecniche di ottimizzazione CEM, tra cui sincronizzazione della frequenza SMPS, ampio spettro, controllo della velocità di risposta, regolazione manuale della frequenza

- Modalità standby a bassa potenza con corrente di riposo molto bassa (35 μA con VPRE e HVLDO ON)

- 2 pin ingresso per il rilevamento della riattivazione e della tensione batteria

- Controllo dispositivo tramite interfaccia I2C con CRC (fino a 3,4 MHz)

- Funzionamento a doppio dispositivo possibile tramite pin di sincronizzazione dedicato

- Portfolio scalabile da QM ad ASIL B e ASIL D con circuiti per il monitoraggio indipendente, interfaccia dedicata per il monitoraggio MCU, semplice funzione watchdog e challenger, power good, ripristino e interruzione, autotest integrato, uscita fail-safe

- Configurazione tramite programmazione OTP

- Abilitazione dei prototipi per supportare le impostazioni personalizzate durante lo sviluppo del progetto in modalità progettazione

- Package QFN56 8,0 mm x 8,0 mm x 0,85; passo da 0,5 mm

Applicazioni

- Gateway

- Infotainment

- ADAS

- Cluster

- V2x

- Radio

- Visione

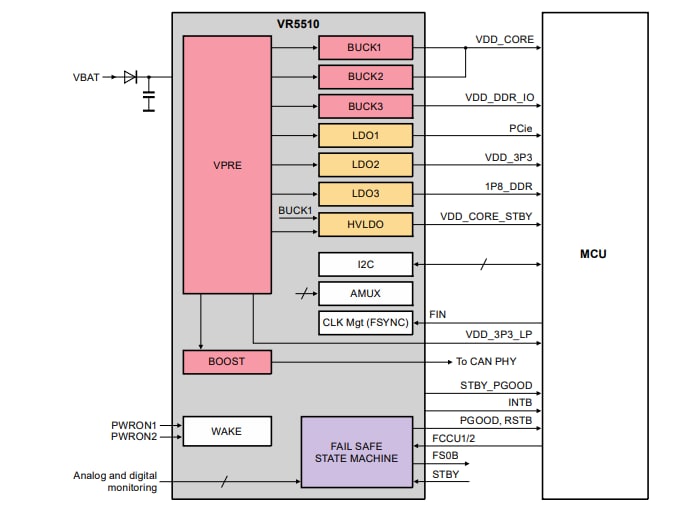

Schema di applicazione semplificato

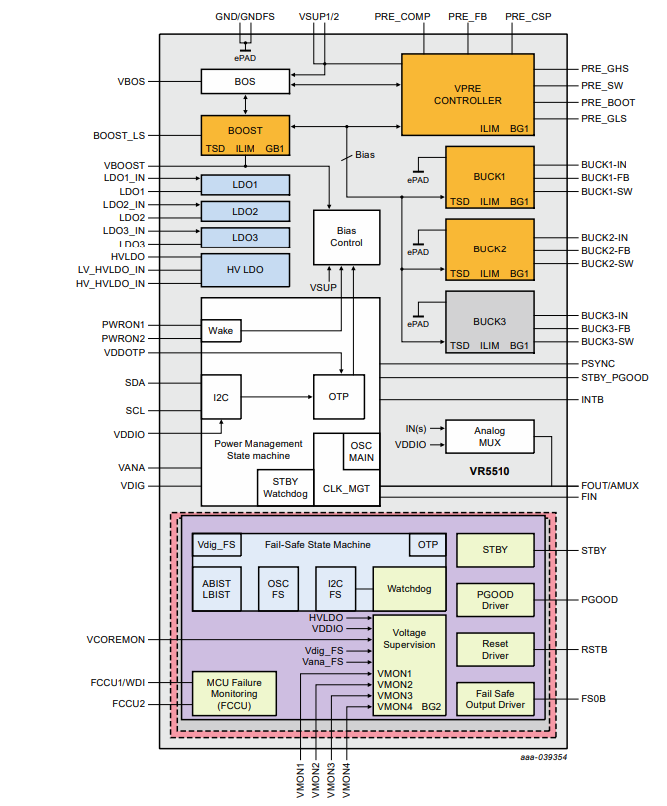

Diagramma a blocchi interno

Profilo del package