Nexperia Buffer/driver di linea singoli di inversione 74LVC1G240

I driver di linea/buffer di inversione singolo 74LVC1G240 Nexperia sono driver di linea/buffer di inversione a 1 bit con un'uscita a 3 stati. Il 74LVC1G240 presenta un OE di abilitazione in uscita, in emissione per consentire uno stato di OFF ad alta impedenza con impostazione HIGH. Un dispositivo da 3,3 V o 5 V aziona gli ingressi per la flessibilità come traslatori in ambienti misti da 3,3 V e 5 V. L'azione a innesco Schmitt a tutti gli ingressi rende il circuito tollerante con i tempi di incremento e riduzione di ingresso più lenti.I driver di linea/buffer di inversione singolo 74LVC1G240 Nexperia sono completamente specificati per applicazioni di spegnimento parziale utilizzando circuiti IOFF. Il circuito IOFF disabilita le uscite, impedendo il riflusso della corrente potenzialmente dannoso attraverso il 74LVC1G240 quando viene spento.

Caratteristiche

- Conforme allo standard JEDEC:

- JESD8-7 (da 1,65 V a 1,95 V)

- JESD8-5 (da 2,3 V a 2,7 V)

- JESD8-B/JESD36 (da 2,7 V a 3,6 V)

- Unità di uscita da ±24 mA (VCC = 3,0 V)

- Protezione ESD:

- L'ANSI/ESDA/JEDEC JS-001 classe 2 HBM supera i 2000 V

- CDM ANSI/ESDA/JEDEC JS-002 classe C3 superiore a 1000 V

- Ampio intervallo di tensioni di alimentazione da 1,65 V a 5,5 V

- Alta immunità al rumore

- Consumo di potenza ridotto CMOS

- Gli ingressi accettano tensioni fino a 5 V

- Le prestazioni a protezione latch-up superano 250 mA

- Interfaccia diretta con livelli TTL

- Specificata da -40 °C a +85 °C e -40 °C a +125 °C

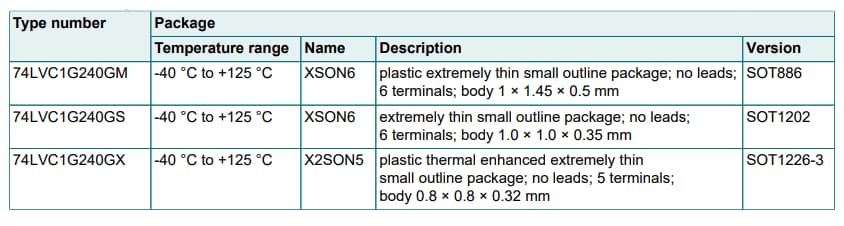

Tabella di confronto parti

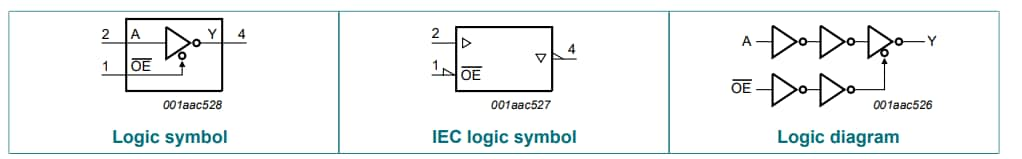

Diagrammi funzionali

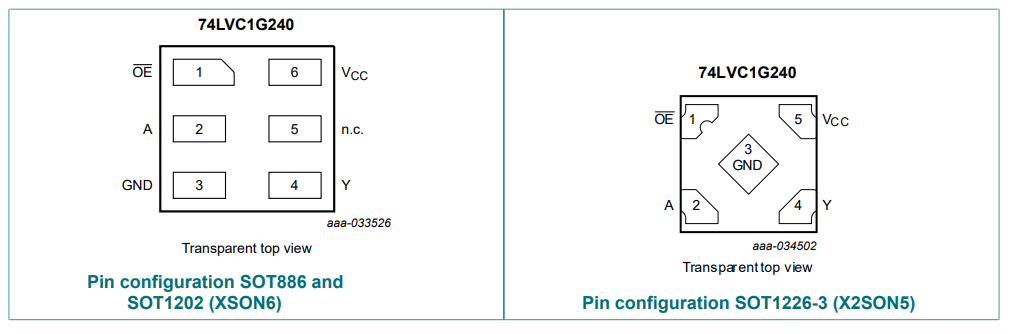

Configurazioni dei pin

Pubblicato: 2022-05-12

| Aggiornato: 2022-08-10