Infineon Technologies MCU per il settore automobilistico a 32 Bit CYT3DL TRAVEO™

Infineon Technologies CYT3DL TRAVEO™ T2G 32-Bit Automotive MCUs are dedicated to automotive systems such as instrument clusters and Head-Up Displays (HUD). The CYT3DL MCUs feature a 2D graphics engine, sound processing, an Arm® Cortex®-M7 CPU running up to 240MHz for primary processing, and an Arm Cortex-M0+ CPU for peripheral/security processing. The MCUs include a WVGA GFX and are available in two unique packages: 216-pin TEQFP and 272-ball BGA. The Infineon TRAVEO T2G CYT3DL family products contain embedded peripherals supporting controller area networks with a flexible data rate (CAN FD), local interconnect networks (LIN), clock extension peripheral interfaces (CXPI), and Ethernet. The devices are manufactured using an advanced 40nm process. The CYT3DL TRAVEO T2G 32-Bit Automotive MCUs incorporate Infineon's low-power flash memory and multiple high-performance analog/digital peripherals and create a secure computing platform.Caratteristiche

- Sottosistema grafico

- Supporta il rendering grafico 2D e 2.5D (alterazione prospettica, effetti 3D)

- Risoluzione di colore interna

- Memoria video ad accesso casuale (VRAM) integrata da 2.048 KB

- 2 interfacce di uscita video che supportano un display da:

- RGB parallelo (dimensione massima dello schermo 1600 × 600 a 40 MHz)

- FPD-link singolo (dimensione massima dello schermo 1920 × 720 a 110 MHz)

- 1x motore di acquisizione per l’elaborazione dell’input video per ingresso ITU 656 o ingresso parallelo RGB/YUV o MIPI CSI-2

- Alterazione immediata dello schermo per applicazioni HUD

- Trasmissione video diretta dall’acquisizione all’interfaccia display con sovrapposizione grafica

- Motore di composizione per la composizione della scena dai layer di visualizzazione

- Motore di visualizzazione per funzioni di generazione di temporizzazione video e di visualizzazione

- Motore di disegno per l’accelerazione del rendering mediante grafica vettoriale

- Command sequencer per la configurazione e il controllo del processo di rendering

- Supporta il rendering grafico senza frame buffer (immediato)

- Interfaccia FPD-Link/LVDS a canale singolo per uscita video con risoluzione fino a HD

- Sottosistema audio

- 4 interfacce time-division multiplexing (TDM, multiplazione a divisione di tempo)

- 2 interfacce PCM-PWM

- Fino a 5 interfacce per generatore audio

- 2 mixer streaming audio PCM con 5 flussi iningresso

- 1 convertitore audio da digitale ad analogico (DAC)

- Sottosistema CPU:

- CPU ARM Cortex-M7 a 32 bit, 240 MHz (max.), con:

- Moltiplicatore a ciclo singolo

- Unità a virgola mobile a singola/doppia precisione (FPU)

- Cache dati 16 KB, cache istruzioni 16 KB

- Unità di protezione della memoria (MPU)

- Memorie locali TCM (Tightly-Coupled Memories): 64 KB istruzioni e 64 KB dati

- CPU ARM Cortex-M0 +a 32 bit, 100 MHz con:

- Moltiplicatore a ciclo singolo

- Unità di protezione della memoria

- Comunicazione tra processori nell'hardware

- 4 controller DMA

- CPU ARM Cortex-M7 a 32 bit, 240 MHz (max.), con:

- Memorie integrate

- code-flash 4.160 KB con un ulteriore 128 KB di work-flash

- SRAM da 384 KB con granularità di conservazione selezionabile

- Motore crittografato

- Supporta l’estensione hardware sicura avanzata (eSHE) e il modulo di sicurezza hardware (HSM)

- Avvio e autenticazione sicuri

- AES: blocchi a 128 bit, tasti a 128/192/256 bit

- 3DES: blocchi da 64 bit, chiave da 64 bit

- Unità vettore che supporta la crittografia a chiave asimmetrica come la crittografia Rivest-Shamir-Adleman (RSA) e quella a curva ellittica (ECC)

- SHA-1/2/3: SHA-512, SHA-256, SHA-160 con dati di ingresso a lunghezza variabile

- Supporta CITT CRC16 e IEEE-802.3 CRC32

- Generatore di numeri casuali (TRNG) e generatore di numeri pseudo-casuale (PRNG)

- Modalità Galois/Contatore (GCM)

- Sicurezza funzionale per ASIL-B

- Unità di protezione della memoria (MPU)

- Unità di protezione della memoria condivisa (SMPU)

- Unità di protezione periferica (PPU)

- Timer watchdog (WDT)

- Temporizzatore di supervisione a multi-contatori (MCWDT)

- Rilevatore di bassa tensione (LVD)

- Rilevamento calo di tensione (BOD)

- Rilevamento sovratensione (OVD)

- Rilevamento sovracorrente (OCD)

- Supervisore di clock (CSV)

- Correzione dell’errore hardware (ECC SECDED) su tutte le memorie fondamentali per la sicurezza (SRAM, flash e TCM)

- Funzionamento a bassa potenza da 2,7 V a 5,5 V

- Modalità attiva a bassa potenza, sleep, sleep a bassa potenza, deep sleep e modalità di ibernazione per una gestione dettagliata dell'alimentazione.

- Opzioni configurabili per un BOD robusto

- Supporto per la riattivazione

- Fino a 4 pin per riattivarsi dalla modalità di ibernazione

- Fino a 61 pin GPIO per riattivarsi dalla modalità DeepSleep

- Generatore di eventi, SCB, timer watchdog e allarmi RTC per riattivarsi da modalità DeepSleep

- Orologi.

- Oscillatore principale interno (IMO)

- Oscillatore interno a bassa velocità (OIL)

- Oscillatore a cristalli esterno (ECO)

- Oscillatore a cristalli (WCO)

- Anello ad aggancio di fase (PLL)

- Anello ad aggancio di frequenza (FLL)

- Oscillatore a cristalli esterno a bassa potenza (LPECO)

- Interfacce di comunicazione

- Fino a 4 canali CAN FD

- Fino a 12 canali SCB (Serial Communication Block) riconfigurabili in runtime, ciascuno configurabile come I2C, SPI o UART

- Fino a 2 canali LIN indipendenti

- Fino a 2 canali CXPI con velocità dati fino a 20 kbps

- interfaccia MAC Ethernet 10/100 Mbps conforme a IEEE-802.3bw

- Interfaccia di memoria seriale (SMI)

- 2 SPI (singola, doppia, quadrupla o ottale), interfaccia xSPI

- Crittografia e decrittografia in tempo reale

- Execute-In-Place (XIP) dalla memoria esterna

- Timer

- Fino a 50 blocchi TCPWM (Timer/Counter Pulse-Width modulator) a 16 bit e32 blocchi TCPWM a 32 bit per il regolare funzionamento

- Fino a 16 timer di generazione di eventi (EVTGEN) che supportano la riattivazione ciclica dalla modalità DeepSleep

- Orologio in tempo reale (RTC)

- Campi Anno/Mese/Data, Giorno della settimana e Ora: Minuto: Secondo

- Formati da 12 e 24 ore

- Correzione automatica dell’anno bisestile

- I/O

- Fino a 135 I/O programmabili

- 4 tipi I/O

- Standard GPIO (GPIO _ STD)

- GPIO migliorato (GPIO _ ENH)

- Controllo motore passo-passo GPIO (GPIO _ SMC)

- I/O standard ad alta velocità con basso rumore (HSIO _ STDLN)

- Potenza

- Regolatori

- Modulo di controllo PMIC

- analogico programmabile

- 1 convertitore A/D SAR

- L’ADC supporta anche 6 ingressi analogici interni:

- Riferimento Banda proibita per stabilire i livelli di tensione assoluta

- Diodo calibrato per calcoli di temperatura di giunzione

- 2 ingressi AUTOBUS AMUX e 2 connessioni dirette per monitorare i livelli di alimentazione

- L’ADC supporta l’indirizzamento di multiplexer esterni

- L’ADC dispone di un sequenziatore che supporta la scansione autonoma dei canali configurati

- I/O Intelligente

- 1 blocco I/O intelligente, in grado di eseguire operazioni booleane sui segnali che vanno da e verso I/O

- Fino a 8 I/O (GPIO _ STD) supportati

- Interfaccia di debug

- Controller e interfaccia JTAG conformi a IEEE-1149.1-2001

- Porta SWD (serial wire debug) Arm

- Supporta la traccia ARM Embedded Trace Macrocell (ETM)

- Compatibile con strumenti standard del settore, GHS MULTI o IAR EWARM per lo sviluppo e il debug del codice

- Opzioni del package

- BGA a 272 ball, 16 mm × 16 mm × 1,7 mm (max.), passo ball 0,8 mm

- TEQFP a 216 ball, 24 mm × 24 mm × 1,6 mm (max.), passo ball 0,4 mm

Applicazioni

- Cluster di strumenti per il settore automobilistico

- Illuminazione anteriore a LED per autoveicoli

- Computer per abitacoli ad alte prestazioni

- Infotainment di bordo per veicoli (IVI) e HMI

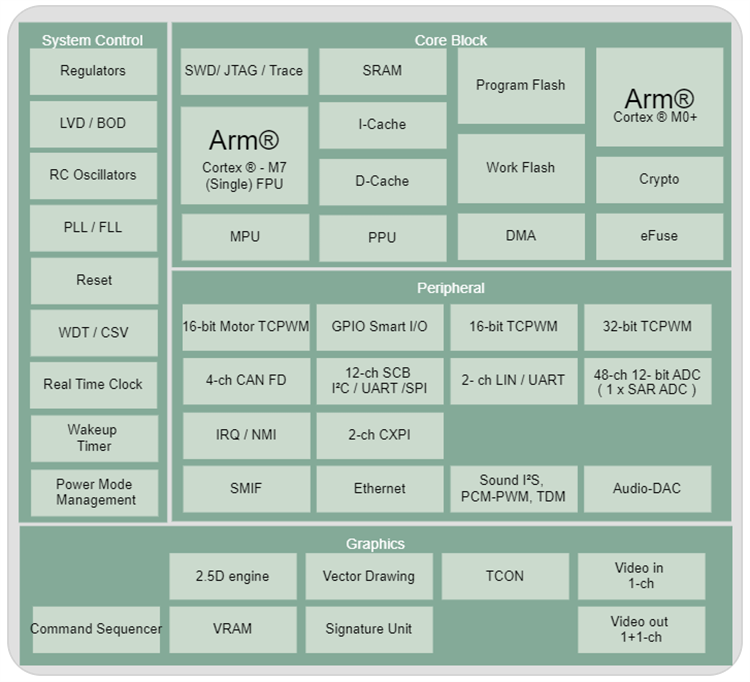

Schema a blocchi

Pubblicato: 2024-09-11

| Aggiornato: 2025-02-28