Infineon Technologies Memoria HyperRAM™ 2.0 S80KS2562 E S80KS2563 da 256 MB

La memoria HYPERRAM™ 2.0 S80KS2562 e S80KS2563 di Infineon Technologies è una RAM dinamica (DRAM) ad alta velocità, a basso numero di pin e a bassa potenza con aggiornamento automatico e un'interfaccia HyperBUS (S80KS2562) o Octal xSPI (S80KS2563). Entrambi i dispositivi presentano una velocità di clock massima di 200 MHz, un throughput di dati fino a 400 Mbps e modalità di sospensione ibrida a risparmio energetico e di spegnimento profondo. Gli HyperRAM S80KS2562 e S80KS2563 sono ideali per l'uso in sistemi integrati ad alte prestazioni che richiedono memoria di espansione scratchpad o buffer.Le interfacce HyperBus e Octal xSPI supportate dai prodotti HyperRAM si basano sulle funzionalità legacy delle memorie di interfaccia parallela e seriale, migliorando al contempo le prestazioni del sistema e la facilità di progettazione e riducendo i costi di sistema.

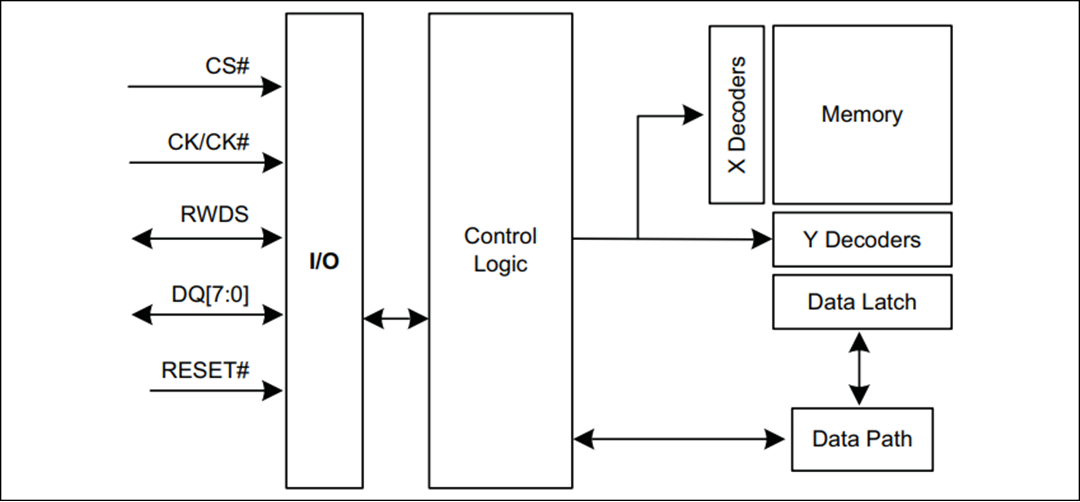

L'architettura a basso numero di pin rende HyperRAM particolarmente adatta alle applicazioni con limiti di potenza e di spazio sulla scheda che richiedono una RAM esterna al chip.

La memoria HyperRAM S80KS2562 e S80KS2563 da 256 MB di Infineon Technologies è disponibile in un package FBGA (Fine-Pitch Ball Grid Array) a 24 sfere.

Caratteristiche

- Tecnologia: DRAM a 25 nm

- Interfaccia

- S80KS2562: interfaccia HyperBUS™

- S80KS2563: interfaccia xSPI (ottale)

- Supporto interfaccia da 1,8 V

- Clock a terminazione singola (CK) con 11 segnali bus

- Clock differenziale opzionale (CK, CK#) con 12 segnali bus

- Selezione chip (CS#)

- Bus dei dati a 8 bit (DQ[7:0])

- Ripristino hardware (RESET#)

- Dati di lettura-scrittura bidirezionali strobe (RWDS)

- Uscita all'inizio di tutte le transazioni per indicare la latenza di aggiornamento

- Uscita durante le transazioni di lettura con strobe di dati di lettura

- Inserimento durante le transazioni di scrittura come maschera dati di scrittura

- Aggiornamento matrice

- Matrice di memoria parziale

- Completo

- Alimentazione

- Consumo di corrente di lettura/scrittura survoltore 22 mA/25 mA

- Modalità di sospensione ibrida

- Modalità spegnimento profondo

- Prestazioni

- Velocità di clock massima di 200 MHz

- Tempo di accesso massimo di 35 ns

- DDR: trasferisce dati su entrambi i bordi del clock

- Throughput dati fino a 400 Mbps (3.200 Mbps)

- Caratteristiche di survoltore configurabili

- Survoltore lineare

- Lunghezza survoltore avvolta

- 16 byte (8 clock)

- 32 byte (16 clock)

- 64 byte (32 clock)

- 128 byte (64 clock)

- Opzione ibrida: un survoltore avvolto seguito da un survoltore lineare

- Forza di azionamento di uscita configurabile

- Package

- Package FBGA-24 da 6,0 mm x 8,0 mm, passo da 1,0 mm

Applicazioni

- Quadri di bordo, sistemi di intrattenimento e telematici per autoveicoli

- Pannelli di visualizzazione HMI industriali e di consumo

- Visione industriale

- Dispositivi indossabili di consumo

- Moduli di comunicazione

Video

Schema a blocchi logici

Pubblicato: 2021-12-29

| Aggiornato: 2023-04-25