BittWare Scheda acceleratrice FPGA XUP-P3R

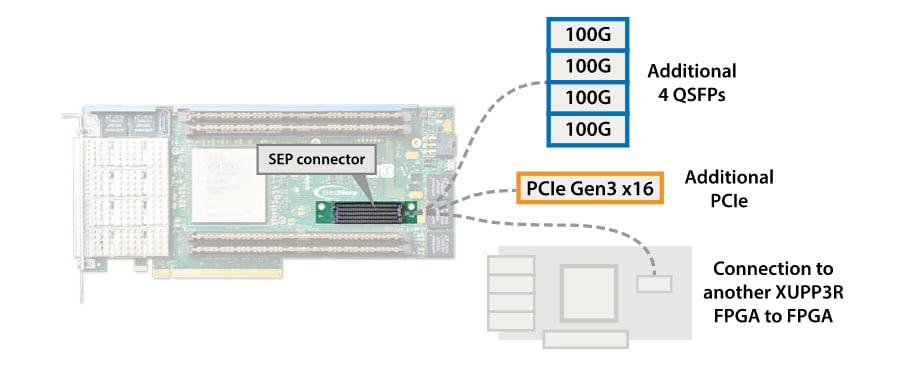

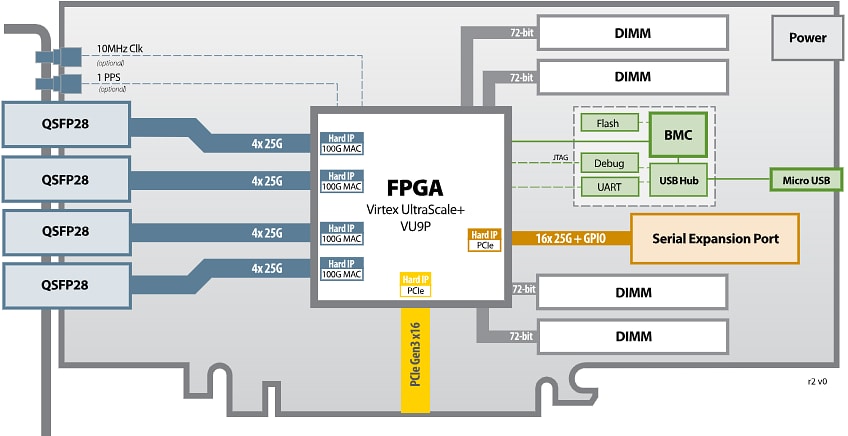

La scheda di accelerazione FPGA XUP-P3R di BittWare è una scheda 3/4-length PCIe x16 basata sull’FPGA UltraScale+ di Xilinx Virtex, che fornisce alte prestazioni, elevata larghezza di banda e latenza ridotta per sistemi che richiedono flusso di dati ed elaborazione dei pacchetti. La scheda XUP-P3R fornisce ampie configurazioni di memoria, incluso il supporto fino a 512 GB, sofisticate opzioni di clock e temporizzazione e quattro gabbie QSFP sul pannello anteriore, ognuna con supporto 100 Gbps (4x25) e 100GbE. La porta di espansione seriale (SEP) consente l’espansione dell' XUPP3R per uno slot PCIe Gen3 x16 aggiuntivo, 4 QSFPs supplementari o il collegamento tra due XUPP3Rs. La scheda di accelerazione FPGA XUP-P3R di BittWare integra un controller di gestione della scheda (BMC) per il monitoraggio avanzato del sistema e la semplificazione dell’integrazione e della gestione della piattaforma. XUP-P3R è ideale per le applicazioni di data center, tra cui elaborazione e sicurezza di rete, accelerazione, archiviazione, trasmissione e SigInt.Caratteristiche

- Ampie configurazioni di memoria, fino a 512 GB DDR4

- Integra BMC per il monitoraggio avanzato del sistema

- 4 100GbE tramite 4 QSFP28

- 2,5 milioni di FPGA LCs da Xilinx fino a VU9P

- Semplifica l’integrazione e la gestione della piattaforma

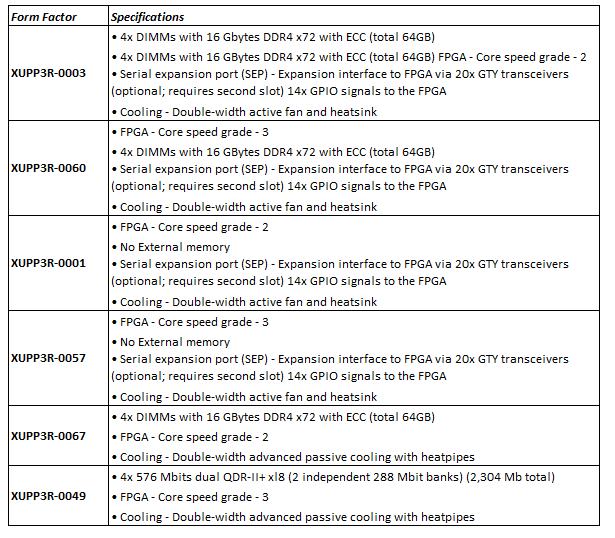

Specifiche

- FPGA

- Virtex UltraScale+ VU9P

- Classe di velocità del nucleo – 2

- Memoria flash integrata per avvio FPGA

- Memoria esterna

- 4 siti DIMM, ciascun supporto

- Fino a 128 GByte DDR4 x72 con ECC

- Fino a 576 Mbits dual QDR-II+ x18 (2 banchi indipendenti da 288 Mbit)

- 4 siti DIMM, ciascun supporto

- Interfaccia host x16 Gen3 direttamente all’FPGA

- Porte Micro USB 2.0 per debug e programmazione FPGA e Flash

- Porta di espansione seriale (SEP)

- Interfaccia di espansione a FPGA tramite ricetrasmettitori GTY 20x (opzionale; richiede il secondo slot)

- 14 segnali GPIO all'FPGA

- Controller di gestione scheda

- Monitoraggio di tensione, corrente e temperatura

- Sequenziamento e ripristino dell'alimentazione

- Aggiornamenti sul campo

- Configurazione e controllo FPGA

- Configurazione clock

- Accesso bus I2C

- USB 2.0

- Override di tensione

- Monitoraggio di tensione, corrente e temperatura

- Sviluppo FPGA

- Gabbie QSFP

- 4 gabbie QSFP28 (zQSFP) sul pannello anteriore collegate direttamente a FPGA tramite 16 ricetrasmettitori

- Ciascuna supporta 100 GbE, 40 GbE, 4 x 25 GbE o 4 x 10 GbE e può essere combinata per 400 GbE

- Raffreddamento

- Ventola e dissipatore di calore attivo a doppia larghezza - standard

- Dissipatore di calore passivo a doppia larghezza - opzionale

- Raffreddamento passivo avanzato a doppia larghezza con tubi di calore - opzionale

- Componenti elettrici.

- Alimentazione integrata derivata da uno slot PCIe 12 V e un connettore AUX (6 pin)

- La dissipazione di potenza dipende dall'applicazione

- Intervallo temperatura di funzionamento da +5 °C a +35 °C

- Fattore di forma

- Scheda a doppio slot PCIe, 3/4 di lunghezza, ad altezza standard

- 9,4 “x 4,37”

- Sviluppo di applicazioni

- HDL/Verilog

- Kit di strumenti BittWorks II – strumenti di host, comando e debug per hardware BittWare

- Suite di progettazione Xilinx Vivado

- OpenCL – ambiente di sviluppo Xilinx SDAccel, Release della piattaforma SDAccel ed esempi pre-integrati per XUP-P3R

- HDL/Verilog

Compliances

• FCC (USA) 47CFR15.107 / 47CFR15.109

• CE (Europe) EN 55032:2015/A11:2020 / EN55024:2010 / EN 55035:2017 / EN 61000-3-2:2014 / EN 610003-3:2013

• UKCA (United Kingdom) BS EN 55032:2012/AC:2013 / BS EN55024:2010 / BS EN 55035:2017 / BS EN 61000-3-2:2014 / BS EN 610003-3:2013

• ICES (Canada) ICES-003 issue 7

• Safety objectives referred to in Article 3 and set out in Annex I of DIRECTIVE 2014/35/EU have been fulfilled

• RoHS compliant to the 2011/65/EU + 2015/863 directive

Video

Grafico di confronto fattore di forma

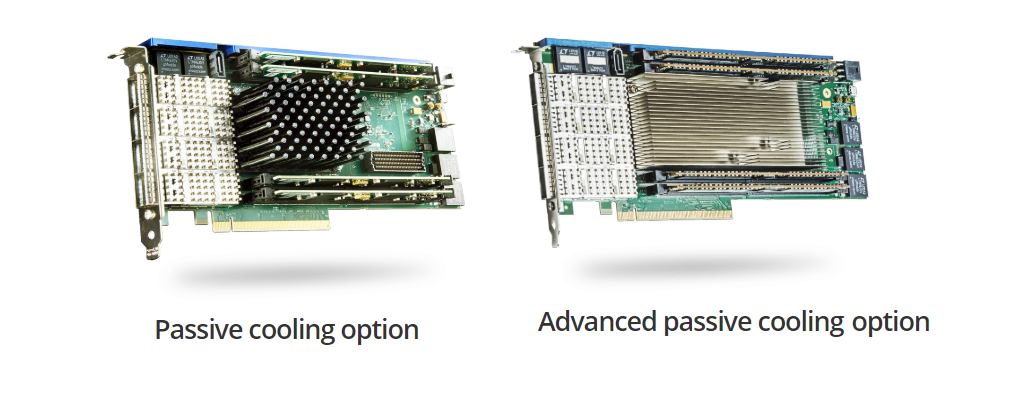

Opzioni di raffreddamento

Schema dei moduli SEP

Schema a blocchi

Infographic

Pubblicato: 2020-06-11

| Aggiornato: 2025-10-15