Analog Devices Inc. Circuiti a blocco di fase (PLL) a N frazionario ADF4383

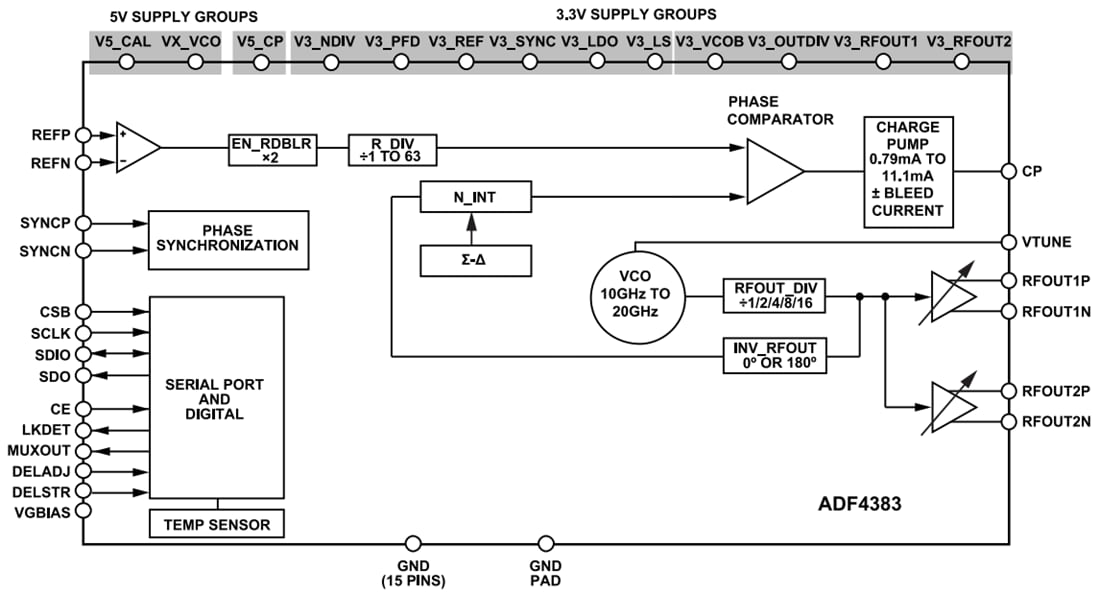

I circuiti a blocco di fase (PLL) a N frazionario ADF4383 di Analog Devices sono circuiti a blocco di fase (PLL) a N frazionario ad alte prestazioni, a jitter estremamente basso, con oscillatore controllato in tensione (VCO) integrato. Sono ideali per la generazione di oscillatori locali (LO) per applicazioni 5G o per applicazioni di clock per convertitori di dati. Il PLL ad alte prestazioni presenta un coefficiente di merito di -239 dBc/Hz, un basso rumore 1/f e un'elevata frequenza del PFD di 625 MHz in modalità intera, consentendo di raggiungere un rumore in banda e un jitter integrato estremamente bassi. L'ADF4383 è in grado di generare frequenze in una portata di ottava fondamentale da 10 GHz a 20 GHz, eliminando la necessità di filtri subarmonici. I divisori di uscita dell'ADF4383 consentono di generare un intervallo di frequenza di uscita completo da 625 MHz a 20 GHz.L'ADF4383 allinea automaticamente l'uscita al bordo di riferimento di ingresso per applicazioni di clock per convertitori di dati multipli, includendo il divisore di uscita nel circuito di retroazione del PLL. È disponibile un ritardo programmabile tra riferimento e uscita con risoluzione inferiore a 1 ps per applicazioni che richiedono un ritardo deterministico o la capacità di regolazione del ritardo. L'abbinamento del ritardo tra riferimento e uscita su più dispositivi e su tutta la temperatura consente un allineamento multichip prevedibile e preciso.

La semplicità dello schema a blocchi dell'ADF4383 di Analog Devices riduce i tempi di sviluppo. Dispone di una mappa dei registri per l'interfaccia periferica seriale (SPI) semplificata, di un ingresso SYNC esterno e di un allineamento multichip ripetibile sia in modalità intera che frazionaria.

Caratteristiche

- Intervallo di frequenza fondamentale del VCO: da 10 GHz a 20 GHz

- Miglioramento del rumore di fase del VCO fino a 3 dB rispetto all'ADF4382

- Jitter RMS integrato a 20 GHz = 18 fs (larghezza di banda di integrazione: da 100 Hz a 100 MHz)

- Jitter RMS integrato a 20 GHz = 31 fs (metodo SNR ADC)

- Specifiche PLL

- Rumore di fase in banda normalizzato: -239 dBc/Hz (modalità intera)

- Rumore di fase 1/f normalizzato: -287 dBc/Hz

- Frequenza di ingresso massima del rilevatore di fase/frequenza: 625 MHz

- Frequenza di ingresso di riferimento: 4,5 GHz

- Spurie tipiche fPFD: -90 dBc

- Tempo di calibrazione del VCO rapido: <>

- Tempo di autocalibrazione del VCO: <>

- Rumore di fase: -156 dBc/Hz a 20 GHz

- Riferimento alle specifiche di ritardo di uscita

- Coefficiente di temperatura del ritardo di propagazione: 0,06 ps/°C

- Dimensioni del passo di regolazione: <>

- Allineamento di fase di uscita multichip

- Alimentatori da 3,3 V e 5 V.

- Supporto dello strumento di progettazione del filtro ad anello ADIsimPLL™

- LGA a 48 terminali, 7 mm x 7 mm

- Temperatura di funzionamento da -40 °C a +105 °C

Applicazioni

- Orologio convertitore di dati ad alte prestazioni

- Infrastrutture wireless (MC-GSM, 5G, 6G)

- Prova e misurazione

Diagramma a blocchi funzionale